Запись страничной таблицы

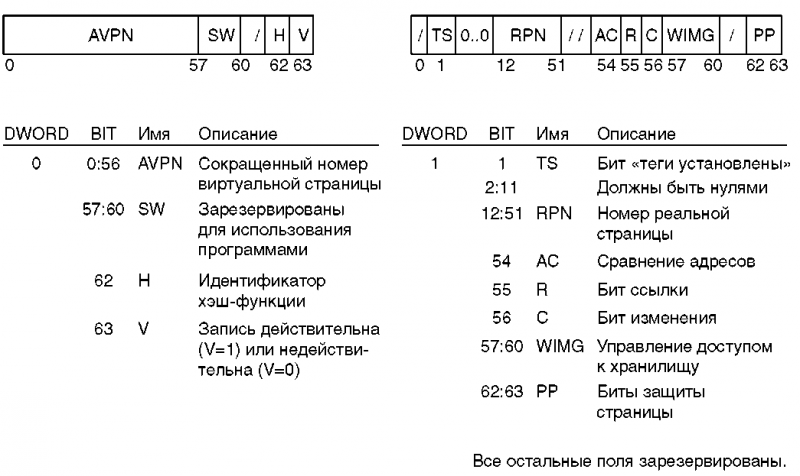

Каждая PTE занимает 16 байтов, как показано на рисунке 8.6. Первое поле каждой записи состоит из 57 разрядов и называется сокращенным номером виртуальной таблицы AVPN (abbreviated virtual page number). Внимательные читатели помнят по рисунку 8.4, что полный VPN содержит только 52 разряда. Как же сокращенная форма может быть длиннее? Дело в том, что архитектура PowerPC разработана для поддержки виртуальных адресов длиной до 80 разрядов. Для 80-разрядного виртуального адреса VPN должен состоять из 68 разрядов, так что 57 разрядов — это действительно сокращенная форма. AVPN может использоваться вместо полного VPN, так как, по крайней мере, 11 младших разрядов VPN применяются хеш-функцией и их повторения не требуется. Вспомните пример с магазином: Sears не был обязан включать последние две цифры номера телефона клиента в форму заказа, так как эти цифры используются хеш-функцией и их не нужно заново проверять при поиске. AVPN для 64-разрядного виртуального адреса в AS/400 составляет лишь 41 разряд, а его старшие 16 разрядов установлены в 0.

Рисунок 8.6. Формат записи страничной таблицы

Все PTE в PTEG последовательно просматриваются для сравнения VPN с виртуальным адресом. Если в одной из PTE обнаружен нужный AVPN и разряд действительности установлен (V=1), то 40-разрядный RPN из этой записи передается аппаратуре адресации памяти, где к нему присоединяется 12-разрядное смещение для получения реального адреса.

Другие биты PTE предоставляют дополнительную информацию о странице. Биты SW зарезервированы для использования компонентом управления памятью SLIC. Бит H определяет, находится ли данная запись в первичной или во вторичной страничной таблице страниц, которые используют несколько различающиеся хеш-функции. Бит TS задает, содержит ли данная страница указатели и, таким образом, имеет некоторые биты тега равными 1. Бит AC, если он включен, приводит в действие механизм сравнения адреса, который позволяет обнаруживать загрузки и сохранения в блок памяти. Аппаратура устанавливает биты R и C в 1 всякий раз при обращении к данной странице (бит R) или при ее изменении (бит C). Оставшиеся биты имеют отношение к режимам доступа и защите страницы (мы рассмотрим их несколько позже).

Следует несколько задержаться на битах R и С. Управление памятью использует их значения для определения страницы, которую следует удалить из памяти, когда возникает страничная ошибка и в память необходимо считать новую страницу. Управление памятью также использует эти разряды: всякий раз, когда другой компонент SLIC или транслированная программа MI запрашивает операции переноса, очистки или сброса.

Для ускорения поиска кандидата на замещение, управление памятью поддерживает «список поиска» всех страничных фреймов, которые могут быть замещены. При страничной ошибке (или при выполнении операций переноса и очистки) управление памятью вначале ищет в этом списке страничный фрейм, для которого оба бита R и С равны 0. Данная комбинация означает, что в недавнем прошлом страница не использовалась и не была изменена — значит, это лучший кандидат на замещение. После замещения страницы все биты R устанавливаются в значение 0. Таким образом, биты R позволяют определить, к каким страницам происходило обращение после последнего замещения страницы. Для тех страниц, которые не использовались недавно, значения R равны 0.

Если алгоритм замещения страницы в процессе просмотра списка поиска обнаруживает страничный фрейм, который был изменен, но давно не использовался (R=0, C=1), то такой фрейм помещается в «список изменений». Когда в этом списке набирается достаточное число страниц, запускаются одна или несколько задач откачки страниц. Страницы записываются на диск и возвращаются в список поиска (с С равным 0), где становятся кандидатами на замещение, если будут снова востребованы. Откачка страниц предотвращает заполнение памяти измененными страницами, к которым давно не было обращений.

Ясно, что поиск по таблице страниц занимает много времени — настолько много, что выполнять его при каждом обращении к памяти слишком накладно. По счастью, если страница недавно была востребована, велика вероятность, что в ближайшем будущем обращение к ней последует снова. Этот принцип лежит в основе использования справочных буферов: если Вы хотите снова использовать данную запись таблицы страниц, храните ее в регистре, чтобы обращение к ней происходило быстро. Для высокой производительности аппаратно поддерживается справочный буфер трансляции (TLB), содержащий PTE, использованные недавно. Поиск в TLB выполняется перед поиском в таблице страниц. Время поиска в TLB очень мало по сравнению с временем поиска в таблице страниц. Обычно, размер TLB достаточно велик, с расчетом, чтобы не менее 95 процентов трансляций выполнялось без необходимости обращения к таблице страниц.

Режимы доступа к памяти

Все обращения к памяти в AS/400 выполняются под управлением четырех битов режима: «Сквозная запись» W (Write Through), «Кэширование запрещено» I (Caching Inhibited), «Когерентность памяти» M (Memory Coherence ) и «Отслеживаемая память» G (Guarded Storage). Одна из характеристик RISC-процессоров — способность программ контролировать аппаратуру. Значения этих четырех разрядов устанавливаются SLIC для обеспечения части такого контроля на уровне страниц. При всех транслируемых обращениях значения разрядов берутся из PTE. Для всех реальных адресов (E=R или при отключенном перемещении) подразумевается, что биты имеют значения 0, 0, 1 и 1. Биты W и I управляют тем, как процессор использует свой кэш данных. Бит M (обычно используется на многопроцессорных системах) задает, должен ли процессор гарантировать когерентность памяти. Бит G контролирует выборку данных и команд вне порядка их следования.

Приведем некоторую дополнительную информацию о назначении каждого из этих разрядов:

1.W (Write Through)— сквозная запись.

Если W=1, то любое изменение кэша данных записывается и в основную память. Этот разряд устанавливается, если данные в основной памяти должны быть постоянно в актуальном состоянии, например, потому что они используются несколькими процессорами. Команды загрузки будут использовать копию данных из кэша, если она там есть. При сохранении будут обновляться копии в кэше и основной памяти.

2.I (Caching Inhibited)— кэширование запрещено.

Если I=1, то доступ выполняется непосредственно к основной памяти. Во время обращения ни данные по этому адресу, ни содержащий их блок памяти не копируются в кэш. Отключение кэширования может быть полезно при последовательной обработке больших блоков данных, которая иначе будет вызывать постоянную смену содержимого кэша.

3.M (Memory Coherence) — когерентность памяти.

Если M=1, то процессор должен гарантированно обеспечивать когерентность данных. Под когерентностью понимают упорядочение операций записи по данному адресу памяти. Дело в том, что для повышения производительности аппаратура управления памятью иногда может записывать данные в память не в том порядке, в котором процессор выдает команды сохранения. Такой механизм может вызвать проблемы, если область памяти совместно используется несколькими процессорами и порядок операций записи в данную область памяти важен. Установка данного бита для страницы упорядочивает операции записи в эту страницу, выполняемые всеми процессорами.

4.G (Guarded Storage) — отслеживаемая память.

Если G=1, то выборка данных и команд вне порядка их следования с данной страницы запрещена. Для более высокой производительности некоторые процессоры могут выполнять команду до того, как это потребуется при последовательном выполнении. Предположим, например, что у некоторого процессора имеется конвейер команд, не занятый в течение данного цикла. Если далее в потоке команд есть подходящая для конвейера, то процессор начнет ее выполнять. Это называется выполнением вне порядка следования. Конечно, машина должна вести себя в соответствии с моделью последовательного выполнения. Если до того момента, когда процессор в нормальном случае дошел бы до команды, выполненной вне порядка следования, происходит переход или прерывание, то состояние процессора должно быть восстановлено так, как если бы он никогда не выполнял эту команду. Иногда поведение области памяти может не соответствовать модели опережающего выполнения. Например, если область памяти используется устройством ввода-вывода, то опережающая запись в нее может вызвать выполнение ошибочной операции. Если SLIC необходимо гарантировать, что подобного не произойдет, то для соответствующей страницы можно включить бит G.